Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

2024-04-01

Allo stato attuale, i servi motori nelle macchine utensili CNC domestiche sono generalmente dotate di encoder incrementali, mentre l'accuratezza degli encoder incrementali non è troppo alta e l'output è segnali paralleli. Per migliorare la sua precisione, è necessario aumentare la progettazione dell'encoder. Difficoltà e aumentare la produzione di segnali paralleli, che non favoriscono la comunicazione a lunga distanza tra il servo unità e l'encoder. Viene utilizzato l'encoder assoluto, tranne per il fatto che la sua precisione è più volte superiore a quella dell'encoder incrementale. La comunicazione seriale ad alta velocità salva le linee di comunicazione per la comunicazione a lunga distanza. All'altra estremità dell'encoder, CPLD e encoder assoluto vengono utilizzati per la comunicazione seriale ad alta velocità. Il CPLD converte quindi le informazioni sull'encoder ricevuto in trasmissione di dati paralleli. Il DSP nell'unità servo esegue il controllo aritmetico. Questo documento fornirà la progettazione di software e hardware di comunicazione seriale ad alta velocità tra CPLD e encoder assoluto .

Progettazione hardware

L'hardware è composto principalmente da tre moduli: alimentazione, CPLD e circuiti periferici e circuito di interfaccia dell'encoder assoluto.

Modulo di potenza

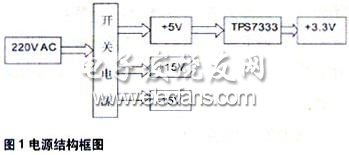

Il modulo di alimentazione è costituito da un circuito di alimentazione di commutazione e un chip di alimentazione CC/CC, come mostrato nella Figura 1.

L'alimentatore di commutazione nella figura converte la tensione della griglia CA 220 V in +5 V, +15 V, -15 V. L'alimentatore di commutazione può filtrare varie interferenze nella griglia di alimentazione e il trasformatore nell'alimentatore di commutazione sarà 220 V CA e l'uscita è + 5 V, + 15 V, -15 V è isolato, il circuito interno utilizza anche TL431 La larghezza dell'impulso di conduzione del tubo dell'interruttore, quindi sono migliori la regolazione anti-interferenza, sicurezza, stabilità e tensione dell'alimentazione di commutazione. Il TPS7333 è un chip DC/DC. La tensione CC +5V viene convertita in una tensione CC stabile di +3,3 V per l'uso da parte del CPLD. Il TPS7333 ha una migliore regolazione di efficienza di conversione, affidabilità e tensione. Può essere utilizzato nell'intervallo di tensione di +3.77V- +10V. La conversione +3.3 V fa bruciare il CPLD a causa della tensione di ingresso troppo elevata.

CPLD e i suoi moduli circuiti periferici

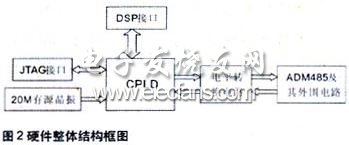

Il CPLD e i suoi moduli circuiti periferici sono composti principalmente da CPLD, circuito di interfaccia di download di programmazione CPLD (interfaccia JTAG), circuito di interfaccia DSP, oscillatore a cristallo attivo, circuito di conversione di livello e ADM485 e i suoi circuiti periferici (circuito periferico responsabile per la comunicazione con l'encota) . figura 2).

Questo design CPLD utilizza EPM570T144C5 di Altera, che appartiene a Max II di Altera. Max II ha un costo inferiore a Max I e consuma meno energia. Il dispositivo ha più celle macro e il ritardo del dispositivo è controllato entro 6 ns. Con prestazioni ad alto costo, l'EPM570T144C5 ha 570 macrocell. Il numero di pin sul chip è 144, di cui 116 sono disponibili porte I/O, quindi le risorse di questo chip sono sufficienti. Il CPLD è principalmente responsabile della comunicazione seriale ad alta velocità con l'encoder assoluto ed è controllato dal comando DSP per inoltrare i dati dell'encoder e altre informazioni al DSP in parallelo.

L'interfaccia JTAG è utilizzata principalmente per scaricare il file eseguibile nel CPLD, installare l'ambiente di sviluppo della società altera - quarto II sul PC e compilare il programma VHDL scritto in questo ambiente di sviluppo per garantire che la compilation non sia senza errori e la funzione è implementata. Collegare il cavo di download all'interfaccia JTAG e scaricare la scheda CPLD tramite lo strumento di download di programmazione fornito da Quartus II.

L'interfaccia DSP è composta da 8 linee di dati, 3 linee di indirizzo e 1 linea di controllo. Le 8 linee di dati sono responsabili del trasferimento dei dati dell'encoder e di altre informazioni. Le 3 righe di indirizzo sono responsabili della trasmissione dei comandi DSP e della decodifica nel terminale CPLD. Il CPLD trasmette i dati dell'encoder o altre informazioni a DSP tramite 8 righe di dati secondo il comando decodificato. La linea di controllo completa principalmente il controllo sincrono del CPLD e del DSP.

L'oscillatore di cristallo attivo da 20 m fornisce principalmente un orologio di riferimento per il CPLD. Sotto la guida del segnale di clock, il CPLD genera una velocità di trasporto di 2,5 Mb/s per comunicare con l'encoder e genera un clock da 10 m Hz per alcuni segnali di controllo logico. Fornire una frequenza di clock di 20 m di Hz richiede una tensione DC da 3,3 V dall'alimentazione.

Il circuito di spostamento di livello è principalmente responsabile della conversione da 3,3 V a 5 V o 5V a 3,3 V, poiché le porte del core e I/O del CPLD richiedono una tensione di alimentazione di 3,3 V, necessaria per ADM485 ed encoder assoluti. Sia la tensione di alimentazione che il circuito del driver della porta I/O sono 5 V, quindi è necessario convertire da 3,3 V in 5 V o 5 V a 3,3 V con il chip di conversione di livello LVC4245A.

ADM485 e i suoi circuiti periferici sono la connessione hardware tra CPLD e comunicazione ad alta velocità dell'encoder assoluto. La tensione di lavoro di ADM485 è 5 V e la sua velocità di comunicazione massima è di 5 MB/s. L'uso di due chip ADM485 per la comunicazione di docking può migliorare la capacità anti-interferenza sulla linea di comunicazione e la distanza di trasmissione più lunga può raggiungere 1,2 km. Il circuito periferico è mostrato nella Figura 3. La metà destra della linea tratteggiata appartiene al circuito periferico dell'encoder assoluto. I resistori a pull-up e pull-down sono 1k ohm, la resistenza di limitazione di corrente è di 220 ohm e l'ADM485 SDAT è il pin di uscita dei dati. ADM485 è SRQ è il pin di input dati, DE di ADM485 è il pin di controllo esterno, questo pin è controllato da CPLD. Poiché il protocollo di comunicazione RS-485 è mezzo duplex, ADM485 può essere nello stato solo di inviare dati o di ricevere dati. Quando ADM485 è DE HIGH, ADM485 è nello stato di output dei dati (ovvero CPLD riceve dati). Quando DE di ADM485 è di basso livello, ADM485 è nello stato di input dei dati (ovvero CPLD invia dati).

Condividi:

Invia domanda

Ms. carol Dong

Numero Di Telefono:86-431-85543703

Fax:86-431---88634119

Mobile:+8613894866263

E-mail:sales@encoders.com.cn

Azienda Indirizzo:333Feiyue Donglu, Changchun City, Jilin Province. China, Changchun, Jilin

mobile Site

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.